先說下CPU的緩存吧,都知道CPU的緩存是分爲L1,L2和L3的,L1又分爲數據緩存和指令緩存,每顆CPU核心都有自己的L1和L2,但L3是各核心共享的,一但涉及共享的東西,當然就有競爭咯。

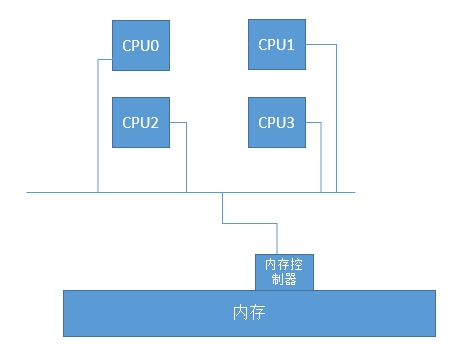

SMP(SymmetricalMulti-Processing,對稱多處理器)架構:

在一個主板上,能放置多顆CPU,例如4顆,如果每顆4核,那麼一共就是16個核心,這種架構存在什麼問題呢?我們設想一下,CPU有多個,但我的內存只有一個,同樣的,內存控制器也是隻有一個的,那麼當我其中的一個CPU去與內存控制器進行交互的時候,其它CPU此時此刻能不能同時與我們的內存控制器交互呢?很顯然,不能了,所以,CPU的顆數越多,那麼資源競爭的越激烈,同樣,性能可能會不容樂觀,所以這種架構一般會隨着CPU的增多,性能可能會逐漸下降。

架構圖類似下圖:

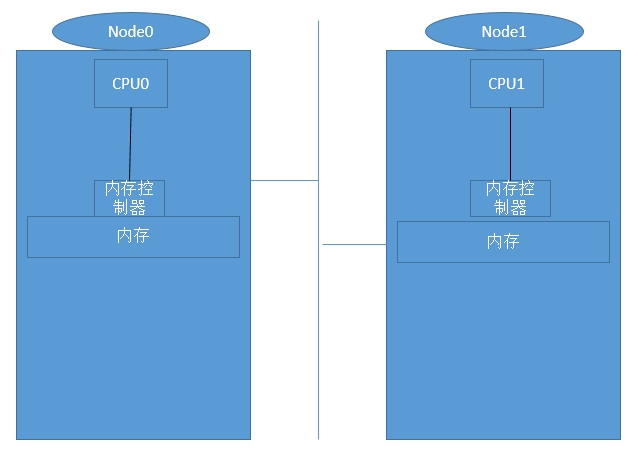

NUMA(Non-Uniform Memory Access Architecture,非一致性內存訪問)架構:

由於SMP架構下,多顆CPU之間搶佔資源較爲激烈,所以NUMA通常有一組CPU(一般爲2顆,可能會更多)和本地內存組成,每一顆CPU都有自己獨有的內存,這樣,就大大避免了多顆CPU之間內存爭用和總線爭用的問題,並且本地CPU和內存間距離較短,傳輸速度及快,但是如果我們要訪問的數據在對方的內存上,這樣,性能就會有所下降,可能會很疑惑,我的本地CPU要訪問的數據怎麼會在對方的CPU上呢?默認情況下,如果我們運行了100個進程,CPU0和CPU1各運行50個進程,當然,進程所佔用的數據還在內存上,過了一會,CPU0結束了10個進程,還運行40個進程,CPU1結束了40個進程,還運行10個進程,此時,CPU根據默認策略,會自動平衡,使兩邊CPU各運行的進程儘可能的一樣多,那麼原來在CPU0上運行的進程就會跑到CPU1上去,那麼當我們再次訪問進程數據時,就會出現交叉內存訪問了。等到下一篇在說如何綁定吧。先看下架構圖吧:

NUMA內存交叉訪問爲什麼速度會慢?

正常情況下CPU訪問一次內存,最快需要3個時鐘週期:

向內存控制器傳輸一個尋址的指令,內存控制器在返回一個值----->CPU確認內存地址,並施加訪問的機制,類似鎖機制----〉進行讀寫操作

在正常情況下訪問如上過程,但出現交叉訪問是如下過程:

向內存控制器傳輸一個尋址指令----〉訪問對方的內存控制器,並施加訪問機制----〉對數據進行讀寫操作

此過程中 由本地內存控制器訪問對方內存控制器需要3個時鐘週期,所以,出現交叉內存訪問會最快會使用6個時鐘週期。