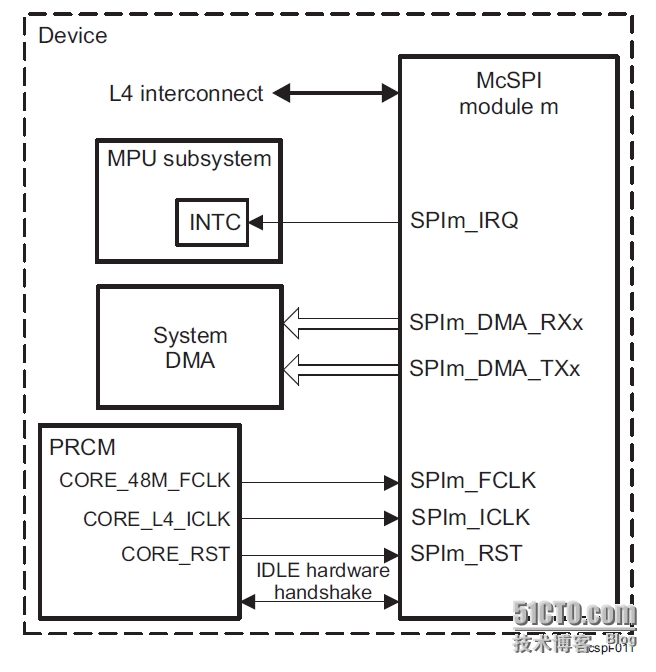

1、Mcspi控制器結構

Spi總線總共有四根信號線(CLK時鐘線,CS片選線,MOSI主設備輸出從設備輸入線,MISO主設備輸入從設備輸出線),其工作過程就是,在clk的控制下,主設備和從設備的兩個雙向移位寄存器進行數據交換。

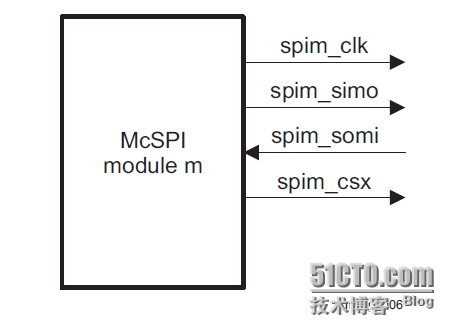

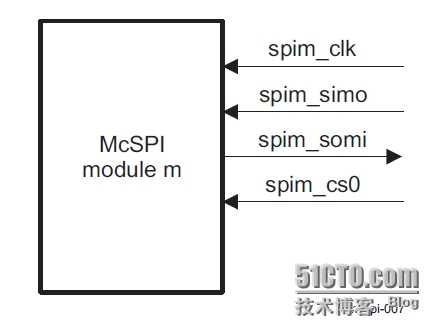

一般CPU內都會集成一個或者多個Mcspi(多通道串行接口)控制器,控制器的內部結構如圖1-1所示,一個控制器有一個或者多個通道,每個通道使用獨立的寄存器,並且每個通道對應兩個DMA請求(讀和寫),一個INTC中斷請求。FCLK是功能時鐘,經過分頻器爲SPI提供工作時鐘CLK(分頻器的值通過寄存器設置),ICLK是總線時鐘,只有該時鐘使能才能對Mcspi控制器裏的寄存器進行讀寫。控制器可以配置爲主設備或者從設備,如下圖1-2和圖1-3所示,時鐘信號和片選信號由控制器內部提供爲主設備,外部提供爲從設備。

Mcspi作爲主設備時,可以配置成單通道工作和多通道工作。在單通道工作下,片選信號可以配置爲自動輸出和軟件控制輸出兩種;在多通道工作下,片選信號只能自動輸出。

圖1-1

圖1-2

圖1-3

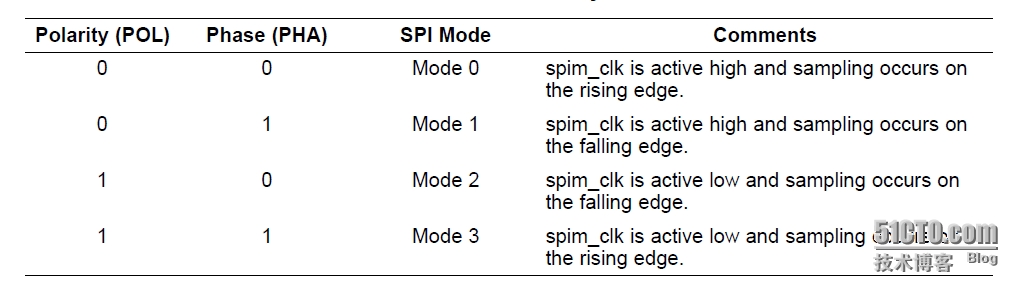

2、Mcspi控制器工作模式

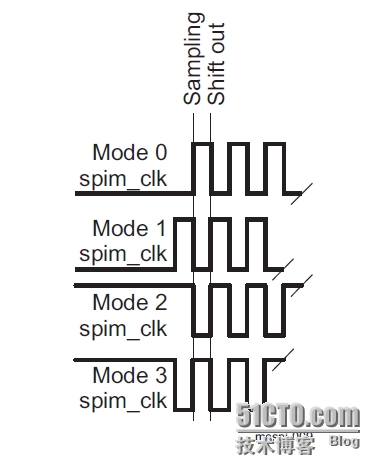

作爲主設備的Mcspi控制器,爲了和外設進行數據交換,根據外設工作要求,主設備輸出的串行時鐘的極性和相位可以配置。如圖2-1和圖2-2所示,共有四種模式。

圖2-1

圖2-2

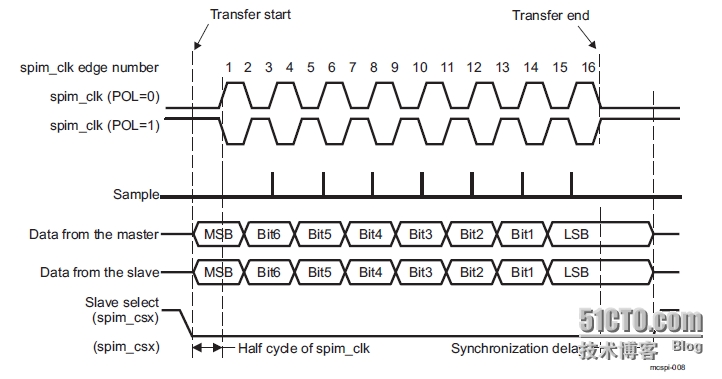

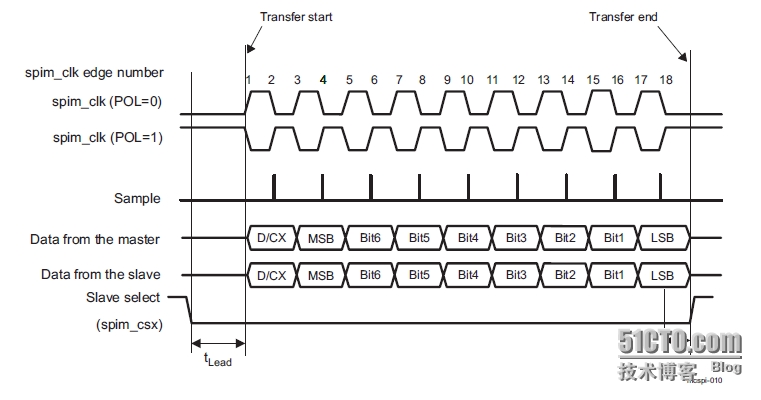

鍾極性用來配置同步時鐘空閒時的狀態,對傳輸協議沒有重大影響,時鐘相位則用來配置spi總線的傳輸協議。如果PHA=0,片選有效後主設備和從設備立刻準備數據(主設備將數據移到MOSI上,從設備將數據移到MISO上),半個時鐘週期後輸出時鐘信號,即在第一個時鐘沿對第一位數據進行採樣,如圖2-3所示;如果PHA=1,片選有效後經過時間tLead開始輸出時鐘信號(tLead的大小可以通過寄存器配置),同時輸出數據,半個時鐘週期後數據準備好,即在第二個時鐘沿對第一位數據進行採樣,如圖2-4所示。

圖2-3

圖2-4

3、使用

在使用時,應該根據從設備支持的模式,將主設備配置成四種模式中的一種。