寄存器

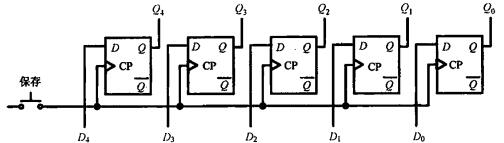

多個數連加,除了一開始,以後每次都有一箇中間結果參與計算,這就需要一個保存中間結果的寄存器。一個觸發器可以保存一個比特。一個寄存器通常由好多個邊沿D觸發器組成。如下圖這個寄存器包含了5個上升沿D觸發器,所有能用來保存一個5比特長的二進制數。

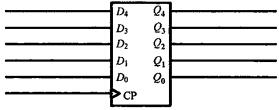

不管一個二進制數包含多少個比特,要保存它,只需要把每一個比特都保存起來即可。所有的觸發器CP端都連在一起,這樣就可以接收同一個控制命令。一旦“保存”開關按下,在CP脈衝的上升沿,所有觸發器同時開始幹活,二進制數的每一位都在同一時間被保存起來,並出現在Qo-Q4上。寄存器符號如下:

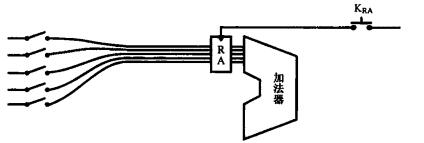

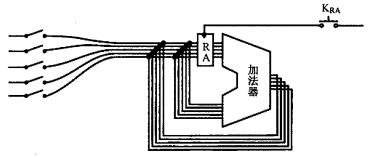

如下圖RA就是寄存器,按鍵開關Kra和RA的CP端相連,當我們用左邊那一排開關板出一個數後,如果按一下Kra,這個數就被鎖住。於此同時,它把自己存儲的內容輸送到加法器,並一直保持,作爲第一個要相加的數。

數字先到達寄存器,再提供給加法器

我們想用同一排開關向加法器提供另一個數,設計電路圖如下:

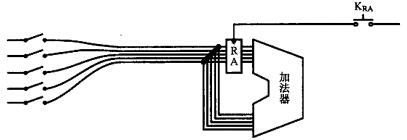

經過改造之後,通過左邊那排開關送進來的數可以到達寄存器RA,同時也被送到加法器的另一個輸入端。取決於你的動機,如果你想把它保存到寄存器RA中,那就按一下開關Kra;如果你想用它和RA中的數相加,就什麼都不做,結果自然從加法器的輸出端呈現。

把輸出結果保存在寄存器,再次改造電路如下:

加法器的計算結果返回寄存器中

上面電路存在如下問題,首先左邊那排開關和加法器的輸出是直接相連的,都要走寄存器RA門前那段路。在邏輯電路里,大家共用線路稱爲總線。如果不考慮電路衝突,計算結果從加法器出來之後,不但會被送往寄存器RA,還會再次進入自己的輸入端,這理所當然地會形成一個反饋,而且是一邊反饋、一邊還在做加法,一切全亂了套。要徹底解決這個問題,就必須重新設計真個電路。一個最簡單地解決方案是使用電子開關,更多的時候,我們也稱之爲傳輸門。