VHDL之Quartus簡介

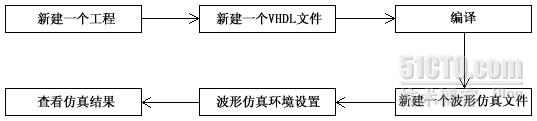

1. 流程

這裏我們使用Quartus8.0來做演示

2. 步驟

1) 新建一個工程

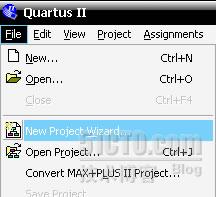

Ø 新建工程

在D:\下新建一個目錄,目錄名爲project

啓動Quartus8.0集成開發環境,選擇【File】->【New project Wizard…】

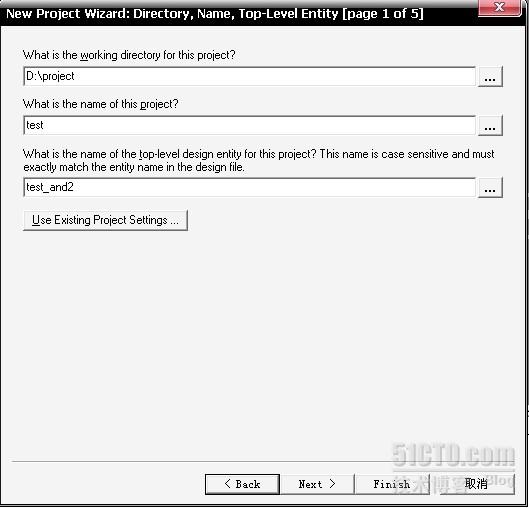

Ø 輸入工程信息

輸入工程保存目錄,工程名爲test。頂層實體名爲test_add2

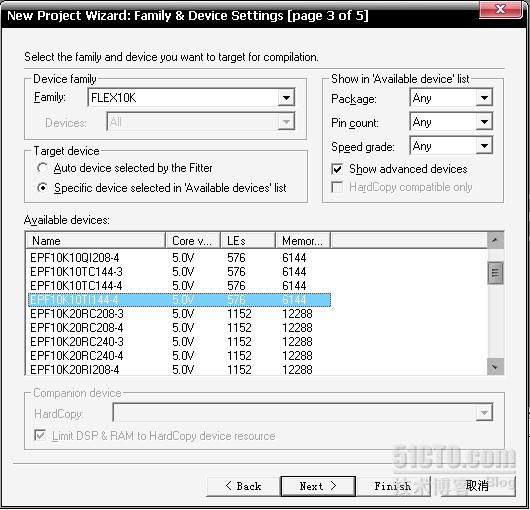

Ø 選擇設備類型

根據所使用的不同的試驗箱選擇不同的器材系列以及型號,這裏使用的是FLEX10K系列中的EPF10K10TI144-4的試驗箱

Ø 完成

單擊“Finish”完成工程文件的建立,可以看到工程框圖中已經有所建立的工程了

2) 新建一個VHDL文件

Ø 建立文件

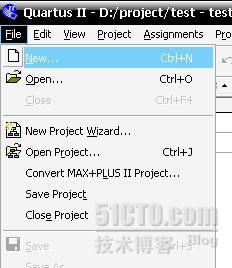

單擊【File】->【New】

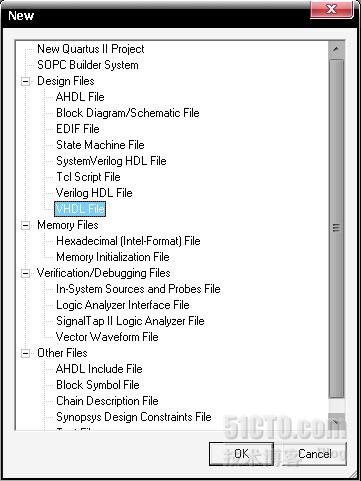

Ø 選擇所建文件類型

選擇VHDL文件

Ø 編寫代碼

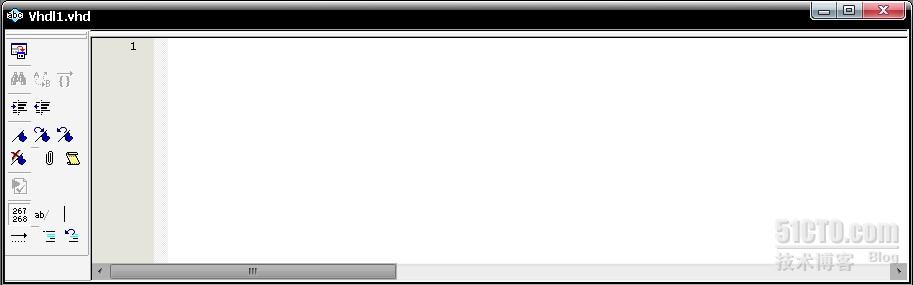

建立好後可以看到所建VHDL文件的編輯框

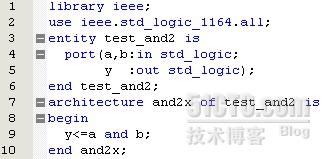

在空白處,輸入VHDL語言程序段

第一行:庫說明語句

第二行:程序包說明語句

第三到第六行:定義三個實體,a、b爲輸入,y爲輸出

第七到第十行:一個結構體,它的功能是與運算,當a、b都爲1時,y值爲1

3) 編譯

編譯通過後出現提示框,表示編譯成功

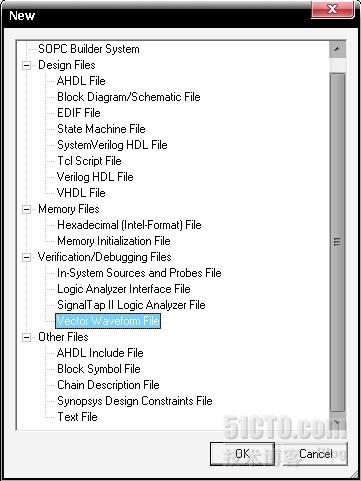

4) 建立一個波形仿真文件

Ø 新建波形仿真文件

單擊【File】->【New】

新建波形仿真文件

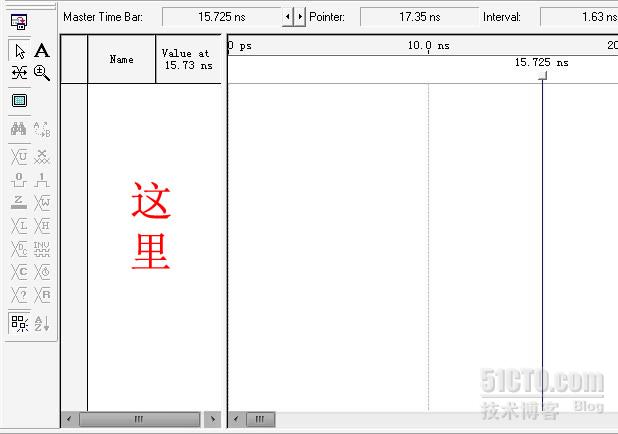

Ø 新建波形圖

在圖紅字處雙擊鼠標左鍵

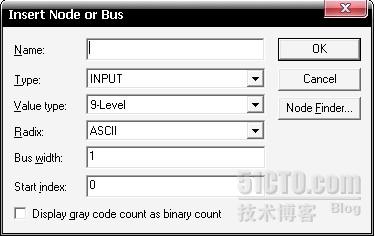

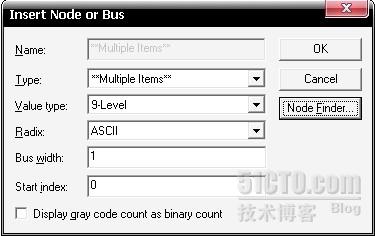

彈出插入節點或總線對話框

Ø 添加端口仿真文件。

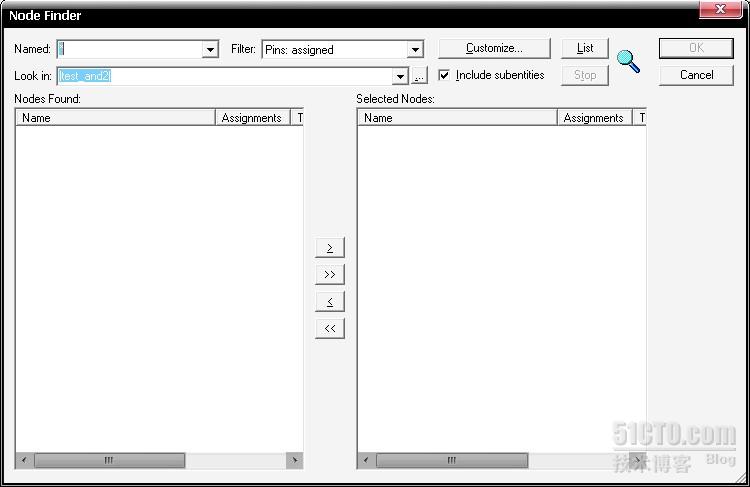

l 單擊“Node Finder”按鈕

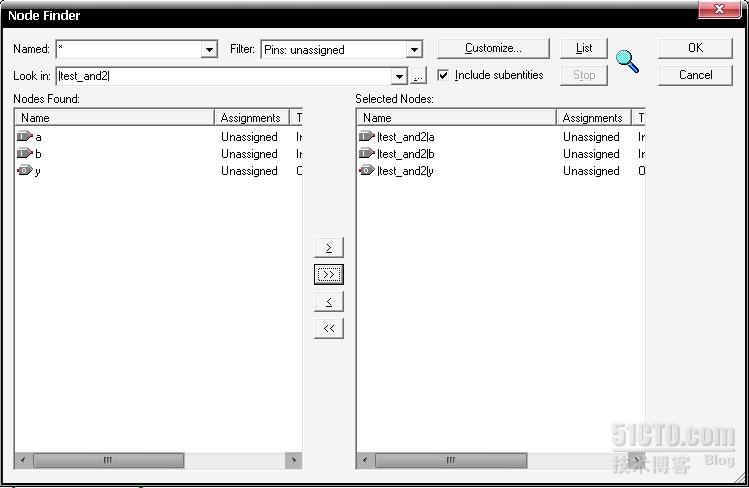

l 查詢所有未配置端口

l 確定選擇

單擊OK即可

Ø 編輯波形仿真文件

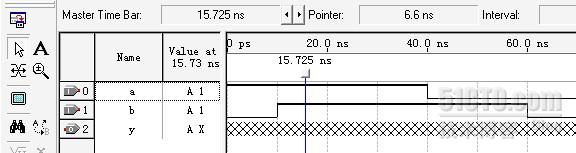

如圖編輯波形仿真文件,並保存

5) 波形仿真環境設置

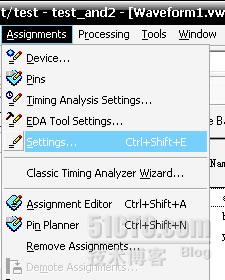

Ø 打開設置:

選擇【Assignments】->【Setting】或在工程文件上單擊右鍵,選擇Setting。

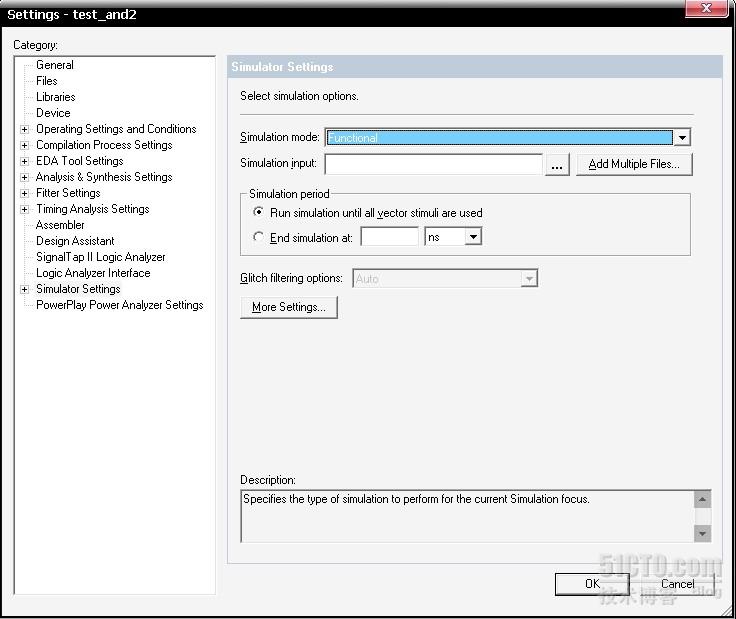

Ø 仿真設置

選擇“simulator setting”,將“simulation mode”改爲“Functional”

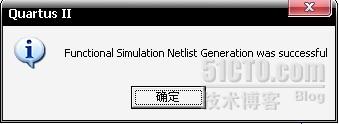

Ø 產生仿真所需的網格

單擊【Processing】->【Generate Functional Simulation Netlist】

Ø 網格產生成功

6) 查看波形仿真結果

查看波形仿真結果,根據所寫的程序,當a,b都爲1時y值爲1,由仿真圖可以看出結果是正確的

發表評論

所有評論

還沒有人評論,想成為第一個評論的人麼? 請在上方評論欄輸入並且點擊發布.