Quartus

使能DEV_CLRn等特殊引腳功能

在bdf文件中檢索網絡net

選中網絡,Ctrl+F,可以查找所需的net!

LogicLock操作步驟

參考:

create new region

創建區域

- 打開邏輯鎖區域Logic Regions窗口 [Alt+L]

2、添加邏輯區域

3、定位邏輯鎖在Chip Planner的區域:

4、將設計模塊適配到新建的Region

5、關閉Optimize I/O 選項

6、編譯設計

7、反標註節點位置[未找到]

Altera建議使用增量式編譯方式而不是使用邏輯鎖,來保持當前的綜合和適配結果!

Incremental Compilation操作步驟

參考:

ModelSim路徑

關閉網絡連接

生成TestBench模版

執行結果:

|

TestBench樣例: |

|

//This is a simple modelSim simulation flow demo //Function: simple testbench of pll_tb.v //2004-12-2 Westor

`timescale 1ns/100ps

module pll_ram_tb ();

reg clk_in; //50MHz reg rst; //asynchronous reset, low-effect reg [7:0] data_in; //data to ram reg wr_en; //wirte enable reg rd_en; //read enable reg [4:0] rd_addr; //read addrress

wire clk_out; //clock output, 100MHz wire lock; //pll lock indicator wire package_full; //indicate the ram is full wire [7:0] data_out; //data to ram

initial begin clk_in = 0; rst = 0; data_in = 8'h55; rd_en = 1'bz; wr_en = 1'bz; rd_addr = 5'b0;

# 500 rst =1;

# 1500 rst =0;

# 1700 rst =1;

repeat (9) write_ram;

repeat (5) read_ram;

repeat (8) begin # 100 write_ram;

# 5 read_ram; end # 8000 $stop; end

always # 10 clk_in =~clk_in;

task write_ram; begin # 5 wr_en = 1; data_in = data_in + 1;

# 20 wr_en = 1'bz; end endtask

task read_ram; begin # 5 rd_en = 1; rd_addr = rd_addr + 1;

# 20 rd_en = 1'bz; end endtask

pll_ram pll_ram_u1(clk_in, rst, data_in, wr_en, rd_en, rd_addr, clk_out, lock, package_full, data_out );

endmodule |

將測試文件添加到工程設置:

重要-注意名稱填寫來自上一步驟生成的vt文件。

波形VWF文件仿真

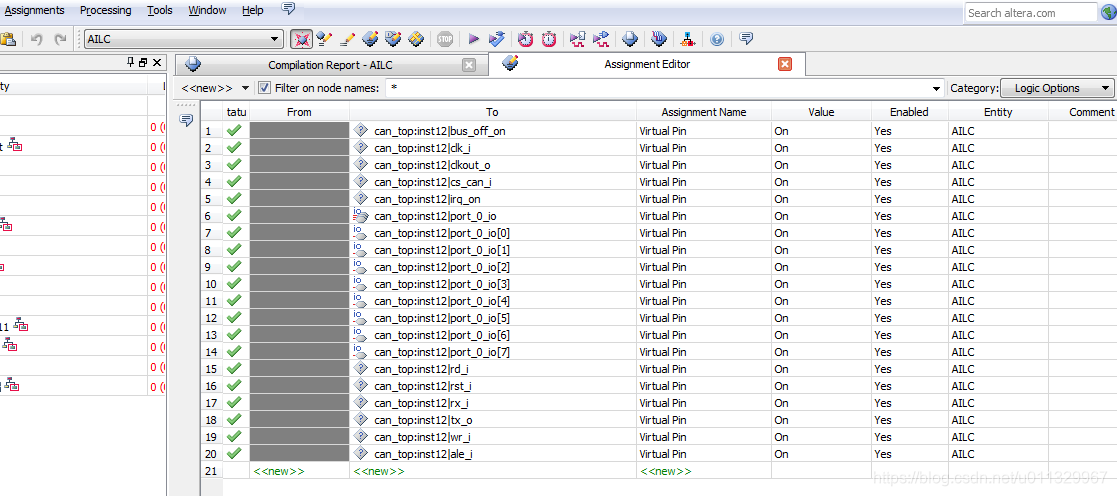

Virtual Pin設置

Quartus II Support for Verilog 2001

編譯結果查看:

需要選中fitter中的summary,才能看到最終的結果:

查看內部寄存器在ModelSim仿真的值:

f1.Maintain Hierachy 設置爲 “on”

f2.使用層次化調用的方法即”.”,添加wire信號到要觀測的寄存器

樣例:wire name = 模塊名.子實例名…端口定義名或寄存器名(一定不能用實例化的實參名)

特殊情況:SISR0寄存器雖然定義爲reg[15:0]但由於某些位沒有驅動,實際生成的網表是按SISR0_0、SISR0_1…來定義的,可以右擊->view declaration在.vo文件查看。

PLL模塊的輸入時鐘一定要和設置的實際輸入時鐘一致否則沒有輸出信號:

根據`timescale 1ns/10ps定義來計算時鐘輸入inclk0。

(1ns是時間單位,10ps是仿真精度)

充分使用模版功能查看verilog運算符功能,以及systemverilog語法:

使用verilog2001構建可定製參數的v文件:

1.使用了generate語法,但是還不屬於systemverilog,systemverilog是verilog的擴展,語法更簡潔更靈活。使用systemverilog可以更改文件後綴名爲.sv或者在verilog HDL input選項選擇SystemVerilog。

2.一開始編譯不成功是因爲使用了`include語句,直接通過Add Files添加到工程即可。否則報錯:…not support synthesizing nested module declaration!這個問題困惑了很久,一隻以爲設置宏parameter參數的格式不對。

3.Genenrate語法一共3種:

Generate語法要求必須有begin,且begin後面必須有name(實例化使用);genvar變量在一個文件中通用不能重複定義,變量名稱不能一樣,begin後面的name名稱也是一樣。

1)If:

2)Case:

2)For:

4、verilog2001的在quartus2的支持:藉助自帶的help文檔,這個功能是需要單獨安裝的在13.0sp1版本quartus.

Quartus/13.0sp1/quartus/common/help/webhelp/master.htm#mergedProjects/quartus/gl_quartus_welcome.htm

5、systemverilog 在 quartus2的支持:

同4.

//-----------------------------------------------------------------------------

wire FANA_flag;

wire FANB_flag;

//`include "fan_det.v"//Wrong:can not add this words,case to false:Not support synthesizing nested module declaration.

fan_det #(2) fan_det_inst

(

.clk(clk),//40mHz

.rst(rst2_n),

.in({FANB_STUS,FANA_STUS}),//fan pin

.out({FANB_flag,FANA_flag}) //state out

);

//---------------------------------------------------------------------------------------------

/*

Detect the fan state.

*/

module fan_det

#(parameter N=1)//the number of the fan.

(

input clk,//40mHz

input rst,

input [N-1:0] in,//fan pin

output reg [N-1:0] out //state out

);

reg clk_div; //0x1A286分頻輸出

reg [15:0] clk_count; //分頻計數器

reg [15:0] min; //一分鐘寄存器

//

reg [N-1:0] FAN_D1; //用於FAN_STUS輸入同步,且轉爲單CLK脈衝

reg [N-1:0] FAN_D2;

wire [N-1:0] FAN_trigger; //風扇單CLK脈衝輸入

//

reg [15:0] FAN_count[0:N-1]; //風扇轉速脈衝計數器

//

assign FAN_trigger = (FAN_D1) & (~FAN_D2);//bit &

always@(posedge clk or negedge rst) //同步

begin

if(~rst)

begin

FAN_D1 <= {N{1'b0}};

FAN_D2 <= {N{1'b0}};

end

else

begin

FAN_D1 <= in;

FAN_D2 <= FAN_D1;

end

end

//SystemVerilog

/*

ACTION: Set the Verilog Input Version for the file to SystemVerilog_2005

or save the file as a SystemVerilog Design File (.sv).

*/

genvar i;

genvar j;

generate

for(i=0;i<=N;i=i+1)

begin:fan_cnt//name

always@(posedge clk or negedge rst)

begin

if(!rst)

FAN_count[i]<=16'h00;

else

begin

if(( min >= 16'h0BEB ) && ( FAN_trigger[i] ))//上電5秒後開始計數,FANA_STUS爲高

FAN_count[i] <= FAN_count[i] + 16'h01;

if( min == 16'h5372 ) //計數35秒後,清零

FAN_count[i] <= 16'h00;

end

end

end

endgenerate

//

generate

for(j=0;j<=N;j=j+1)

begin:fan_cout//name

always@(posedge clk or negedge rst)

begin

if(!rst)

out[j] <= 1'b0;

else

if( ( min >= 16'h5370 ) && ( min<=16'h5372 ) )

begin

if(FAN_count[j] >= 12'h3E8) //半分鐘分扇發出的脈衝大於1000個

begin

out[j] <= 1'b0;

end

else

begin

out[j] <= 1'b1; //小於風扇轉速過低標誌位置高

end

end

end

end

endgenerate

endmodule

UDP使用:

不可忽略的警告:

1、使用第三方EDA工具仿真PLL需要1ps的時間單位:

- Warning (202000): An incorrect timescale is selected for the Verilog Output (.VO) file of this PLL design. It's required that the timescale should be 1 ps when simulating a PLL design in a third party EDA tool.

2、unsafe behavior 暗指毛刺glitch:

3、Modelsim Altera performance:

輔助編輯器Notepad++:quartus自帶的編輯器功能有限,唯一特色就是具有Template功能

1、分欄功能使用:

左擊文件的標籤頁不放拖到空白處,放開後選擇“複製到另一視圖”

右擊分頁線選擇旋轉可以改變分欄方向

2、更改文本的編碼,在quartus中顯示中文:

3、層次摺疊及快捷鍵:

摺疊快捷鍵推薦”ALT+2”

4、快速打開文件所在的文件夾:

5、帶顏色代碼粘貼功能:

先選中要粘貼的代碼,再選擇”插件->NppExport->Copy RTF tp clipboard”

6、值得推薦的自帶Template功能:

芯片驗證UVM方法:

仿真分類:

Testbench參考模板:

光標定位設置:

add wave語法:

|

add wave -hex -group CONTROL \ /AILC_vlg_tst/i1/inst3/inst2/CONTROL_15 \ /AILC_vlg_tst/i1/inst3/inst2/CONTROL_14 \ /AILC_vlg_tst/i1/inst3/inst2/CONTROL_13 \ /AILC_vlg_tst/i1/inst3/inst2/CONTROL_12 \ /AILC_vlg_tst/i1/inst3/inst2/CONTROL_11 \ /AILC_vlg_tst/i1/inst3/inst2/CONTROL_10 \ /AILC_vlg_tst/i1/inst3/inst2/CONTROL_9 \ /AILC_vlg_tst/i1/inst3/inst2/CONTROL_8 \ /AILC_vlg_tst/i1/inst3/inst2/CONTROL_7 \ /AILC_vlg_tst/i1/inst3/inst2/CONTROL_6 \ /AILC_vlg_tst/i1/inst3/inst2/CONTROL_5 \ /AILC_vlg_tst/i1/inst3/inst2/CONTROL_4 \ /AILC_vlg_tst/i1/inst3/inst2/CONTROL_3 \ /AILC_vlg_tst/i1/inst3/inst2/CONTROL_2 \ /AILC_vlg_tst/i1/inst3/inst2/CONTROL_1 \ /AILC_vlg_tst/i1/inst3/inst2/CONTROL_0

|

force語句:

在兩個仿真器中,force保持一個值直到它被release,而一個deposited值保持其值僅到信號更新。在Verilog-XL中, force命令使force節點減速,但可以在一個表達式和一個信號之間創建一個連續關係。它可以爲一個位或部分賦值,而$deposit只能影響整個線網或寄存器。

使用相對NativeLink路徑:

使用這種方式路徑比較乾淨易於查看,沒有特殊符號產生。

自定義仿真腳本

先使用自動生成,拷貝修改後改爲自定義,可以保留自己需要的波形及仿真操作:

同時關閉自動sim腳本生成功能,否則腳本回循環不能定位到上圖指定的腳本:

關於路徑空格報錯:

有3種解決方式:

1、

2、在空格前加反斜槓

3、使用花括號

仿真文件:

VCD

Wlf文件

do文件

Task & event:

$monitor:

Toggle Leaf Names:

ModelSim保存波形設置:

synthesis preserve:

這個命令不適用於端口,適用於內部邏輯,只要實際用到了該reg基本可以保留,

一般找不到(在modelsim的列表裏查找)是因爲雖然定義了實際沒有使用到,被優化掉了。

引腳配置修改QSF文件:

Quartus裁剪:

Dsp builder 安裝:

32位 dsp builder 安裝步驟 2018.11.25 wuhou

先安裝matlab,再重新安裝dsp builder:

1、合併兩個license文件,並新建LM_LICENSE_FILE路徑在用戶和系統環境變量

2、替換目錄下的兩個dll,原先的dll改爲bk

C:\altera\13.0sp1\quartus\dsp_builder\bin

驗證:找一個自帶的demo,雙擊看是否可以編譯及Export:

Dsp builder Path設置:

查看引腳配置類型:

FIR IP核使用測試:

簡介:

在時域中,FIR濾波器的輸入/輸出就是一個輸入信號與單位脈衝相應的卷積。離散方程爲y(n)=x(n)*h(n)=∑x(k)h(n-k)=∑h(k)x(n-k),其中y(n)爲濾波輸出,x(n)爲採樣數據,h(n)爲濾波抽頭係數.設計FIR濾波器就是要找到N個係數。N-1階濾波器通常需要N個係數描述,通常需要N個乘法器和N-1個2輸入加法器實現。根據FIR表達式,濾波器實質上就是進行乘累加運算,乘累加的次數由濾波器階數決定。其串行結構如圖:

對於濾波器的因數也可以用Matlab的FDATool工具得到,一般可在DSP程序中使用,對於FPGA可直接使用自帶的IP 核。

實驗參數:

36階,16位無符號數據輸入,帶通(2.5K~7.5K),採樣頻率設爲20KHz,可以設置輸入通道數,這裏選擇了1個作爲測試,可視具體情況而定。

Matlab仿真文件說明:

一共四個文件,其中output.txt爲執行之後的輸出文件,主文件如下所示爲fir_1_model.m直接運行即可看到濾波器效果。主要用來驗證FIR濾波因數的正確性。

重要使用說明:

1、Quartus13.0在32位上可以使用FIR IP核,但64位電腦不行,對於64位電腦建議使用15.0版本。

2、同時對應的IP核需要對應的破解文件,否則仿真會報錯,license見附錄。

3、對於signal tap文件打開卡頓時由於你編譯次數太多,保留了太多log,導致文件很大,建議刪去。

4、想要讀取ram模塊內容時建議先打開 ,把文件下載到FPGA,再打開

直接監控或者

讀取狀態並設置自己想要的標誌位。Ram模塊可以讀取也可以通過Jtag寫入注意選擇正確的更新圖標,不要弄反了^_^。

5、大的工程儘量分開爲幾個小工程編譯,否則時間太耗費了。

6、IP核的目錄在

EPCQ:

時序分析:

1、打開時序分析工具tools->TimeQuest Timing Analyzer

2、建立時序網表Netlist->Create Timing Netlist

3、新建sdc文件並編輯,插入Create Clock約束【告訴時序分析輸入時鐘的頻率大小】,完全不需要手寫任何代碼

關於高版本打開低版本產生的錯誤警告可以通過修改qsf文件屏蔽