Xilinx的7系列FPGA和Zynq器件在片上集成了模數轉換器和相關的片上傳感器(內置溫度傳感器和功耗傳感器),可在系統設計中免去外置的ADC器件,有力地提高了系統的集成度,在7系列FPGA裏,除了少數spartan系列的低端FPGA沒有XADC外,其它所有的7系列FPGA裏都有XADC模塊。本文就這一新模塊的使用進行簡單介紹,希望對大家有所幫助,當然如有不當之處還請高手指正,以免誤導大家,歡迎大家補充。

其中的用戶指導見xilinx的官網,具體見UG480:7 Series FPGAs and Zynq-7000 SoC XADC Dual 12-Bit 1 MSPS Analog-to-Digital Converter。

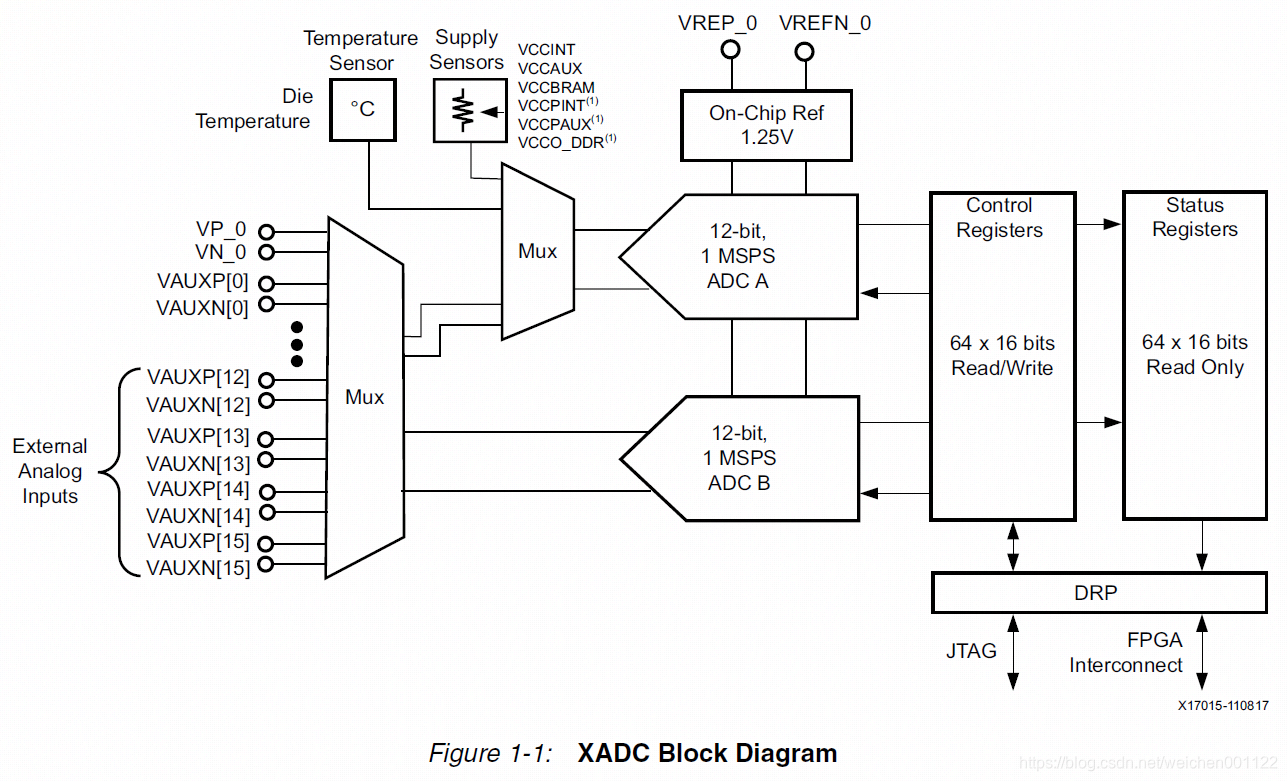

XADC包含2個通道的模擬差分輸入、每個通道的採樣率都爲1MSPS,其功能模塊如下圖所示:

**1、功能框圖**

從上圖可以看出,XADC默認監測FPGA內的溫度以及所有的電壓,還可以接收來自FPGA專用模擬差分管教VP_0\VN_0的模擬差分信號,還可以接收FPGA其他普通數字\模擬混合管腳VAUXP\VAUXN[15:0]的16路模擬差分輸入,因此XADC可以最多處理17路外部模擬信號。

XADC的輸出通過JTAG口可以直接被FPGA開發工具讀取並實時監測,並且藉助Xilinx CORE Generator還可以生成XADC的IP核,加載到FPGA邏輯代碼裏,隨時供用戶讀取FPGA的溫度、電壓等信息。

2、XADC Pinout Requirements模塊管腳需求

所有的XADC模塊的專用管腳都屬於Bank0,所以都加上後綴_0,上圖1-2表示了XADC的基本輸入輸出需求:上面有兩種配置需求,左邊使用的是Vccaux(1.8V)供電,並且使用外部的1.25V的參考源,使用外部參考源在精度和熱漂移方面可以獲得更好的性能,且使用一個磁珠用以隔離模擬地和數字地,以避免模擬和數字共地而把噪聲帶入模擬電路;右邊使用的是片內的參考源,此時,VREFP腳必須按照圖示連接到地。

下表列出了XADC Package的管腳

注:XADC模塊有一專用的支持差分輸入的模擬通道輸入引腳(VP/VN),另外還最多有16個輔助的模擬通道輸入引腳(ADxP or ADxN,x爲0到15),Kintex-7不支持輔助通道6,7,13,14,15。Zynq-7000 AP SoC器件由於封裝不通可能不會支持所有的輔助通道,具體要查詢封裝文件。

3、基本使用方法

3.1 XADC模塊的操作方式:

最基本的操作模式叫缺省模式,缺省模式下XADC模塊專用於監視芯片上的供電電壓和芯片溫度,這時XADC模塊並不需要用戶對其進行配置。

另外一個爲同步採樣模式,按預定的步驟順序採樣兩個外部的模擬輸入信號,並把採樣結果存儲在狀態寄存器內。

單通道模式,在這種模式下,用戶必須通過寫控制寄存器40H的CH4到CH0比特來選擇一個要採樣的通道。另外控制寄存器40H的BU(analog input mode) 和ACQ(settling time )兩個參數也必須設置。

獨立ADC模式,在這種模式下, ADC A是固定用來實現一個類似於缺省模式的“監控模式”,報警輸出功能是有效的,用戶必須設置正確的報警門限; ADC B只能用來測量外部的模擬輸入。

Single Pass 模式,在這種模式下,按用戶選擇的採樣順序序列順序採樣一遍後停止ADC。採樣順序序列是由用戶寫序列通道選擇寄存器48H和49H 來設定的。

Continuous Sequence 連續序列模式,這種模式和Single Pass 模式很相似,區別是採樣完一遍後系統自動重新開始序列採樣,故爲連續採樣。

模式選擇是由控制寄存器41H 的SEQ3到SEQ0比特決定,具體如下圖示:

3.2 XADC primitive

XADC模塊的使用方法, 一是直接用FPGA JTAG專用接口訪問, 這時XADC模塊工作在缺省模式; 二是在設計中例化XADC模塊,這是可以通過FPGA邏輯或ZYNQ器件的PS到ADC模塊的專用接口訪問。例化XADC模塊有兩種基本形式:一是ISE 和PlanAhead 環境下LogiCOREIP核的形式調用, 二是EDK環境下對LogiCOREIP核的調用。這兩種調用方法相信對使用過XILINX 產品的朋友來說操作界面與步驟都很熟悉,這裏就不贅述了,主要是想說明下XADC模塊原語,以期對這模塊有個基本的瞭解。下圖是XADC模塊的輸入與輸出端口的示意圖:

其各個管腳的功能描述見下表:

4、PCB設計要點:

模數轉換器所能獲得的精度和PCB設計關係很大,因爲模數轉換器是敏感的部件,它的模擬接口容易受到噪聲的影響,下面就PCB設計時要注意的地方做一簡單介紹。

1). 典型應用中VREFP 和 VREFN外接1.25V 參考電壓,電壓精度爲± 0.2% ,並且在PCB上要儘可能的靠近VREFP 和VREFN引腳,並且按電源IC 要求使用合適的去耦電容。

2). 如果使用片內的參考電壓, VREFP 和 VREFN引腳要通過一磁珠連到模擬地,以去除高頻干擾。

注意隔離數字電源和模擬電源的磁珠應使噪聲對模擬電源供應的波動小於1 LSB (250 uV),這在用12 比特測量時可以最小化噪聲對精度的影響。作爲一個通用原則,模擬地和數字地要分開,以減少噪聲從地平面耦合過來的影響。

3). 儘量在每個引腳放一個100nF 的去耦電容, PCB上儘量靠近引腳。

4). 外接1.25V 參考電壓接VREFP 和 VREFN引腳時, PCB上應該用緊密耦合的差分對形式佈線,它們應該走線在同一層,使用最小間隔,可以用模擬電源和模擬地來隔離保護它。

5). 外部模擬輸入引腳採用差分輸入形式可以有效地去除共模噪聲,兩個差分輸入應該按緊密耦合的差分對形式佈線,使用最小間隔,推薦在輸入端應該放置抗混疊濾波器,這個抗混疊濾波器應該儘可能地靠近FPGA。

6).在單極性輸入時,需要設置ADC爲相應的工作模式,且需要配置一個共模電壓,如下圖所示:

7).在雙極性時,如下圖:

5、寄存器設置

以上爲XADC設置的相關寄存器,0x40-0x43爲配置寄存器,0x43-0x47爲工廠保留測試寄存器,0x48-0x4f爲通道選擇寄存器;0x0-0x5f爲alarm報警信號寄存器。

注意:The read/write operation is not valid or complete until the DRDY signal goes active.

This design assumes an external 50 MHz clock is used for DCLK, and the XADC isconfigured to monitor temperature, supply voltages, and activate alarms if safe limits are exceeded.

XADC #(

// Initializing the XADC Control Registers

.INIT_40(16’h9000),// Calibration coefficient averaging disabled

// averaging of 16 selected for external channels

.INIT_41(16’h2ef0), // Continuous Sequencer Mode, Disable unused ALMs,

// Enable calibration

.INIT_42(16’h0400),// Set DCLK divider to 4, ADC = 500Ksps, DCLK = 50MHz

.INIT_48(16’h4701),// Sequencer channel - enable Temp sensor, VCCINT, VCCAUX,

// VCCBRAM, and calibration

.INIT_49(16’h000f), // Sequencer channel - enable aux analog channels 0 - 3

.INIT_4A(16’h4700),// Averaging enabled for Temp sensor, VCCINT, VCCAUX,

// VCCBRAM

.INIT_4B(16’h0000),// No averaging on external channels

.INIT_4C(16’h0000),// Sequencer Bipolar selection

.INIT_4D(16’h0000),// Sequencer Bipolar selection

.INIT_4E(16’h0000),// Sequencer Acq time selection

.INIT_4F(16’h0000),// Sequencer Acq time selection

.INIT_50(16’hb5ed),// Temp upper alarm trigger 85°C

.INIT_51(16’h5999),// Vccint upper alarm limit 1.05V

.INIT_52(16’hA147),// Vccaux upper alarm limit 1.89V

.INIT_53(16’h0000),// OT upper alarm limit 125°C using automatic shutdown

.INIT_54(16’ha93a),// Temp lower alarm reset 60°C

.INIT_55(16’h5111),// Vccint lower alarm limit 0.95V

.INIT_56(16’h91Eb),// Vccaux lower alarm limit 1.71V

.INIT_57(16’hae4e),// OT lower alarm reset 70°C

.INIT_58(16’h5999),// VCCBRAM upper alarm limit 1.05V

.INIT_5C(16’h5111),// VCCBRAM lower alarm limit 0.95V

.SIM_MONITOR_FILE(“sensor_input.txt”)

// Analog Stimulus file. Analog input values for simulation

)

XADC_INST ( // Connect up instance IO. See UG480 for port descriptions

.CONVST(GND_BIT), // not used

.CONVSTCLK(GND_BIT), // not used

.DADDR(DADDR_IN[6:0]),

.DCLK(DCLK_IN),

.DEN(DEN_IN),

.DI(DI_IN[15:0]),

.DWE(DWE_IN),

.RESET(RESET_IN),

.VAUXN(aux_channel_n[15:0]),

.VAUXP(aux_channel_p[15:0]),

.ALM(alm_int),

.BUSY(BUSY_OUT),

.CHANNEL(CHANNEL_OUT[4:0]),

.DO(DO_OUT[15:0]),

.DRDY(DRDY_OUT),

.EOC(EOC_OUT),

.EOS(EOS_OUT),

.JTAGBUSY(), // not used

.JTAGLOCKED(), // not used

.JTAGMODIFIED(), // not used

.OT(OT_OUT),

.MUXADDR(), // not used

.VP(VP_IN),

.VN(VN_IN)

);

6、XADC值的相關計算

6.1 ADC的計算公式:

6.2 溫度傳感器的計算:

6.3 FPGA的電壓檢測

7、寄存器接口

8、使用XADC IP核

使用DRP接口採集6路模擬通道電壓VP0,VP1,VP5,VP6,VP8,VP9和溫度。

8.1、Basic設置

注意:Analog sim File Option中的Waveform Type要選擇sin,不然仿真頂層文件會跟我的不一致!!!!

8.2、ADC Setup

8.3、Alarm

8.4、通道設置:6路模擬通道電壓VP0,VP1,VP5,VP6,VP8,VP9和溫度

IP的GUI界面相信大家都會配置,可是問題就是IP核生成了,我們如何爲使用呢?還是老方法,IP核生成後,我們先去生成一個Example:

我們看到生成的IP核Example頂層接口是這樣的,並沒有看出來如何對IP的接口使用,沒關係,別急

我們打開xadc_wiz_0_tb仿真頂層文件,

代碼如下: (注意:在GUI界面仿真應該選擇sin波形,否則仿真頂層代碼不是這樣)

從這個頂層代碼基本就能知道接口怎麼用了,我們把代碼整合一下,去除不能綜合的代碼,整理後如下:

有tb文件整理過後的代碼基本就能進行通道電壓的數據採集了,其它通道以此類推。下面是我實際上板測試用debug抓到的數據,我用到的是4、5、6、7、13、14通道。

另外還需要注意的是,我們用戶端得到得是ADC的code值,我們還需要將它換算成電壓值。

總的來說XADC還是比較容易實現的,另外需要注意一點的是在ddr的IP核中mig_7series_0中有調用xdma選項,一般情況下不能同時使用多個xdma,否則編譯會報錯,提示例化了多個xdma!!!!!如果項目中有單獨使用xdma且mig_7series_0也有使用的時候,在mig_7series_0中應該disable xdma,此時應該將單獨使用xdma的IP中採集的溫度數據送給mig_7series_0裏面去。

[1].Xilinx UG480: 7 Series FPGAs and Zynq-7000 AllProgrammable SoC XADC Dual 12-Bit 1 MSPS Analog-to-Digital Converter User Guide

[2].Xilinx UG772: LogiCORE IP XADC Wizard User Guide

[3].Xilinx PG019: LogiCORE IP AXI XADC (v1.00.a) Product Guide

[4]. Xilinx UG585: Zynq-7000 All ProgrammableSoC Technical Reference Manual

[5].Xilinx XAPP554: XADC Layout Guidelines